昨年旧フリスクケースサイズの超小型SDR受信機FriskSDRを試作しました。少々無謀なプランでしたが、当初の目論見通り無事に動作させることができました。ただ、さすがに小さすぎで、製作していただいたりするにはハードルが高過ぎでした。もうすこし常識的なサイズの設計も欲しいと思っていたので、今回あらたに基板を作ってみることにしました。Nanoより大きいので、CentSDR(仮称)としています。

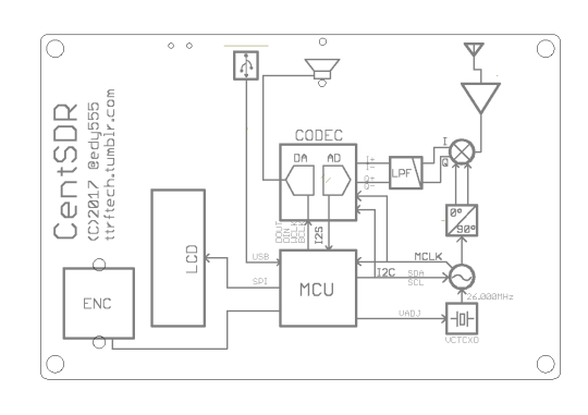

受信機としての基本的なアーキテクチャはFriskSDRとまったく同じです。ローカル発振器としてSi5351aを使い、ジョンソンカウンタで2相信号を作成、アナログマルチプレクサをミキサとして使います。

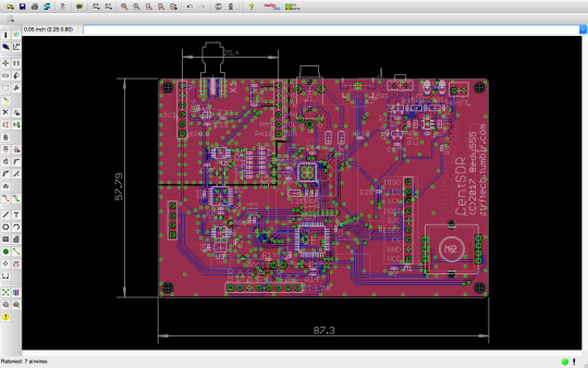

もともと53x27mmの基板サイズに詰め込んでいたものを、大きな基板(といっても58x88mm)にゆったりと再配置した感じです。使っている主要な部品はSMDの同じものです。

ディスプレイはカラーグラフィックLCDを採用することにしました。LPC-Link2やNanoVNAで使ったSPI LCD(ILI9431)が実績があるので、またこれを使ってみることにします。操作はロータリーエンコーダのワンノブスタイルです。

MCUは、FriskSDRと同じくSTM32F303の予定です。実時間処理しながらグラフィック描画をするにはMCUが非力ですが、全く不可能というわけではないはずです。

FriskSDRではCodec TLV320AIC3204のADCの前段にあるVGAのみをアンプとして使っていました。シンプルな構成で、たしかに受信機として動作させることはできていたのですが、正直ゲイン不足であることは否めませんでした。そこで今回は、ゲインブロックを追加で一段置いてみることにしました。さらに、RF入力部にはプラグインモジュールを挿せるようにしておいて、アンプを入れたり、フィルタやミキサを置いたりなど、いろいろ実験できることを目論んでいます。

基板の裏面にはシルクでブロック図を描いてみました。表側には対応する部品が載っています。絵に描いたような実装で、眺めるだけで原理がわかると良いなと思っています(ただ、図として見ると、信号の流れが右→左と少し違和感があります)。実験をしやすいよう各信号にアクセスするパッドを各所に設けてみました。パッドとブロック図がちゃんと対応しています。

ソフトウェアはこれからですが、まずは実績のあるChibiOSベースのものを移植することになると思います。

基板はすでに発注して、製造は完了したようです。試作が進んだらまたご報告したいと思います。

実は明日からのMakerFaireTokyoに出展予定です。今回のプロジェクトも展示したいと思っていたのですが、残念ながら輸送が間に合いませんでした。なので今回は新作の実物は展示が無いのですが、資料や、これまで作ったFriskSDRやNanoVNAご覧いただけます。もしお時間ありましたら、是非、東京ビッグサイトへ。ブースの場所はE08-06です。

参考

- MakerFaireTokyo 2017 https://makezine.jp/event/mft2017/